## Design 4-bit even parity generator.

## Solution:

Let us assume that a 3-bit message is to be transmitted with an even parity bit. Let the three inputs A, B and C are applied to the circuit and output bit is the parity bit P. The total number of 1s must be even, to generate the even parity bit P.

The figure below shows the truth table of even parity generator in which 1 is placed as parity bit in order to make all 1s as even when the number of 1s in the truth table is odd.

| 3-bit message |   |   | Even Parity bit generator (P) |

|---------------|---|---|-------------------------------|

| А             | В | С | Υ                             |

| 0             | 0 | 0 | 0                             |

| 0             | 0 | 1 | 1                             |

| 0             | 1 | 0 | 1                             |

| 0             | 1 | 1 | 0                             |

| 1             | 0 | 0 | 1                             |

| 1             | 0 | 1 | 0                             |

| 1             | 1 | 0 | 0                             |

| 1             | 1 | 1 | 1                             |

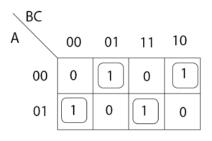

The K-map simplification for 3-bit message even parity generator is

$$P = \bar{A}\bar{B}C + \bar{A}B\bar{C} + A\bar{B}\bar{C} + ABC$$

$$= \bar{A}(\bar{B}C + B\bar{C}) + A(\bar{B}\bar{C} + BC)$$

$$= \bar{A}(B \oplus B) + A(\overline{B \oplus C})$$

$$P = A \oplus B \oplus C$$

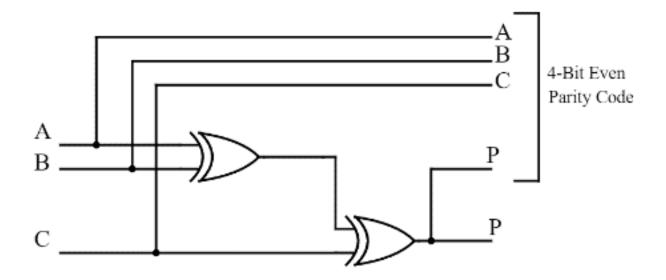

The above expression of even parity generator can be implemented by using two Ex-OR gates as shown in fig.